Etude des circuits logiques combinatoires pour le niveau universitaire.

I) Etude d’un comparateur binaire.

1.1) Principe de base

Le principe consiste à comparer d’abord les bits les plus significatifs ( Most Significant Bit ou M S B) . S’ils sont différents, il est inutile de continuer la comparaison. Par contre s’ils sont égaux, il faut comparer les bits de poids immédiatement inférieur et ainsi de suite.

Organigramme pour deux mots de deux bits.

Remarque : On peut donc réaliser un comparateur à l’aide de circuits logiques.

1.2) Présentation du circuit intégré HEF 4585 B

Le circuit intégré HEF 4585B permet de comparer deux mots de 4 bits ( A3à A0 et B3à B0).

Ce circuit possède trois sorties : - A supérieur à B : O A>B

- A inférieur à B : O A<B

- A égal à B : O A=B

Trois entrée d’extension ( I A>B , I A<B , I A=B ) permettent la mise en cascade de plusieurs circuits afin d’effectuer un comparaison sur des mots plus grands.

Montage de base et fonctionnement.

1.3) Réalisation d’un comparateur 12 bits.

La réalisation d’un comparateur 12 bits nécessite l’emploi de trois comparateurs montés en cascade. La mise en cascade est conditionnée par la lecture de la table de vérité qui indique quelles sont les entrées prioritaires.

Montage :

Explications :

Pour permettre les comparaisons, les entrées d’extension des positions de plus faible poids doivent être connectées comme suit : I A=B et I A>B = 1 , I A<B = 0 .

Pour des mots supérieurs à quatre bits, les circuits peuvent être mis en cascade en connectant I A<B à O A<B , I A=B à O A=B et I A>B à 1.

II) Codeur - Décodeur.

2,1) Etude d'un codeur ou Encodeur.

C'est un circuit à N entrées dont une seulement est active et qui délivre sur n sorties (en code binaire ou autre) le numéro de l'entrée.

2.2) Etude d'un décodeur. (sélecteur de sortie).

C'est un circuit à n entrées qui permet de sélectionner une sortie parmi N ( avec N 2n ).

2.3) Application :

a) Réalisation d’un décodeur 1 parmi 32 :

On dispose de décodeurs 3 vers 8 du type 74 LS 138, donner le montage.

b) Réalisation d’un décodeur 1 parmi 256 :

On dispose de décodeur 4 vers 16 du type 74 LS 154, donner le montage.

2.4) Capteurs codés.

Il s'agit de capteurs fournissant en sortie des informations binaires sous forme de mots binaires de plusieurs bits.

2,4,1) Claviers.

Ensemble d'interrupteurs commandés manuellement pour communiquer des informations ou des ordres à une machine.

a) Disposition matricielle.

On pourrait concevoir des claviers comme un ensemble de touches commandant autant d'interrupteurs qui seraient traités individuellement.

On réalise une économie de connexions en adoptant

la disposition ci-contre dite : "matricielle".

X + Y fils suffisent pour connecter X . Y fils.

Ex : X = 4, Y = 5 9 fils pour 20 touches

A partir de cette disposition, différentes méthodes

ont été proposées pour générer un code binaire

différent pour chacune des touches :

c'est ce qu'on appelle le "codage du clavier".

b) Codage binaire.

Lorsque les touches du clavier sont destinées à entrer des chiffres, (ex : portier à code) on fait suivre le clavier, à disposition matricielle, d'un codeur binaire dont le rôle consiste à délivrer en sortie, le code binaire du nombre correspondant à la touche enfoncée.

Ce code est verrouillé sur les sorties du codeur, ce qui signifie qu'il reste stable jusqu'à ce qu'une nouvelle touche soit enfoncée.

Chaque fois qu'une nouvelle touche est pressée, le codeur envoie un signal dit de "STROBE", afin d'inviter le système auquel le code est destiné à venir le prendre en compte. (Ce signal peut être aussi désigné par "DA : Data Available", ou par "signal d'invitation").

Exemple : Voir codeur de clavier 74 C 922.

c) Code ASCII. (American Standard Code for Interchange of Informations)

On appelle claviers ALPHANUMERIQUES, les claviers dont les touches représentent des nombres et des chiffres sur les machines à écrire ou les ordinateurs ...

Pour représenter l'ensemble des caractères graphiques, un code est quasiment universellement adopté, c'est le code ASCII. Il utilise 7 bits pour représenter l'ensemble des caractères et commandes.

2,4,2) Roues codeuses (commutateurs rotatifs).

Ce sont des commutateurs actionnés à la main qui permettent :

- de générer le code binaire de tout nombre * entre 0 et 9 en BCD;

* entre 0 et F en hexa.

- d'afficher le nombre correspondant sur leur face avant.

Un élément comporte 5 broches : 4 pour les bits 1-2-4-8 et un pour le commun.

Il existe deux types de roues codeuses.

Ces deux montages fournissent des codes complémentaires.

On peut associer plusieurs roues codeuses afin de pouvoir coder des nombres plus importants.

Exemple : Heures, Minutes, Secondes.

Des butées empêchent les chiffres des dizaines de dépasser 5.

L'ensemble de 2 roues codeuses

décimales fournit une information

binaire sur 8 bits :

00 à 99 décimal

Il existe des roues codeuses

héxadécimales (0 à F).

Deux roues fourniront, en sortie, tous les octets de 00 à FF soit de 0 à 255

2.4.3) Capteurs de position par codeurs rotatifs ou linéaires.

Ce sont des systèmes permettant de repérer avec précision la position d'un objet sur un déplacement linéaire (capteurs de translation) ; ou circulaire (capteurs de rotation ou rotatifs).

Dans chacun de ces deux types on distingue : - les capteurs incrémentaux.

- les capteurs absolus;

a) Capteur de rotation incrémental.

Le principe consiste à rendre solidaire de l'objet en déplacement, une gravure en noir et blanc, éclairée par un faisceau visible ou invisible (infra-rouge) et dont la réflexion est lue par un photo-transistor. Les transitions noir-blanc et blanc-noir créent des signaux permettant le repérage.

Le système de lecture possède trois capteurs optiques (photo-diodes et photo-transistors) qui permettent d’obtenir : - un top Zéro (repère unique sur un tour)

- 2 signaux décalés de 90°, voies A et B et éventuellement leurs compléments

III) Etude d'un transcodeur binaire réfléchi / binaire naturel.

Ce type de circuit permet de convertir une position codée en binaire réfléchi (voir codeur de position) en un nombre binaire correspondant à cette position.

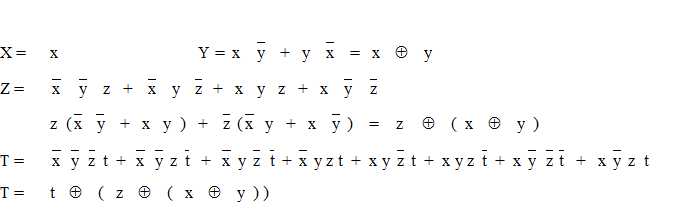

Equations :

Logigrammes:

Remarque : Nous voyons apparaître une structure répétitive qui permet d’étendre à n bits ce système de transcodage.

Application sur le transcodage: Décodeur DCB / 7 segments.

IV) Etude des multiplexeurs et des démultiplexeurs.

Multiplexeur : Sélecteur de données

Demultiplexeur : Répartiteur de données

Le sélecteur de données est un circuit qui à partir d'une adresse binaire (n bits) va sélectionner l'une des 2n entrées pour la mettre en communication avec la sortie.

Le répartiteur est un circuit qui à partir d'une adresse binaire (n bits) va aiguiller l'entrée vers l'une des 2n sorties.

Multiplexeur Démultiplexeur

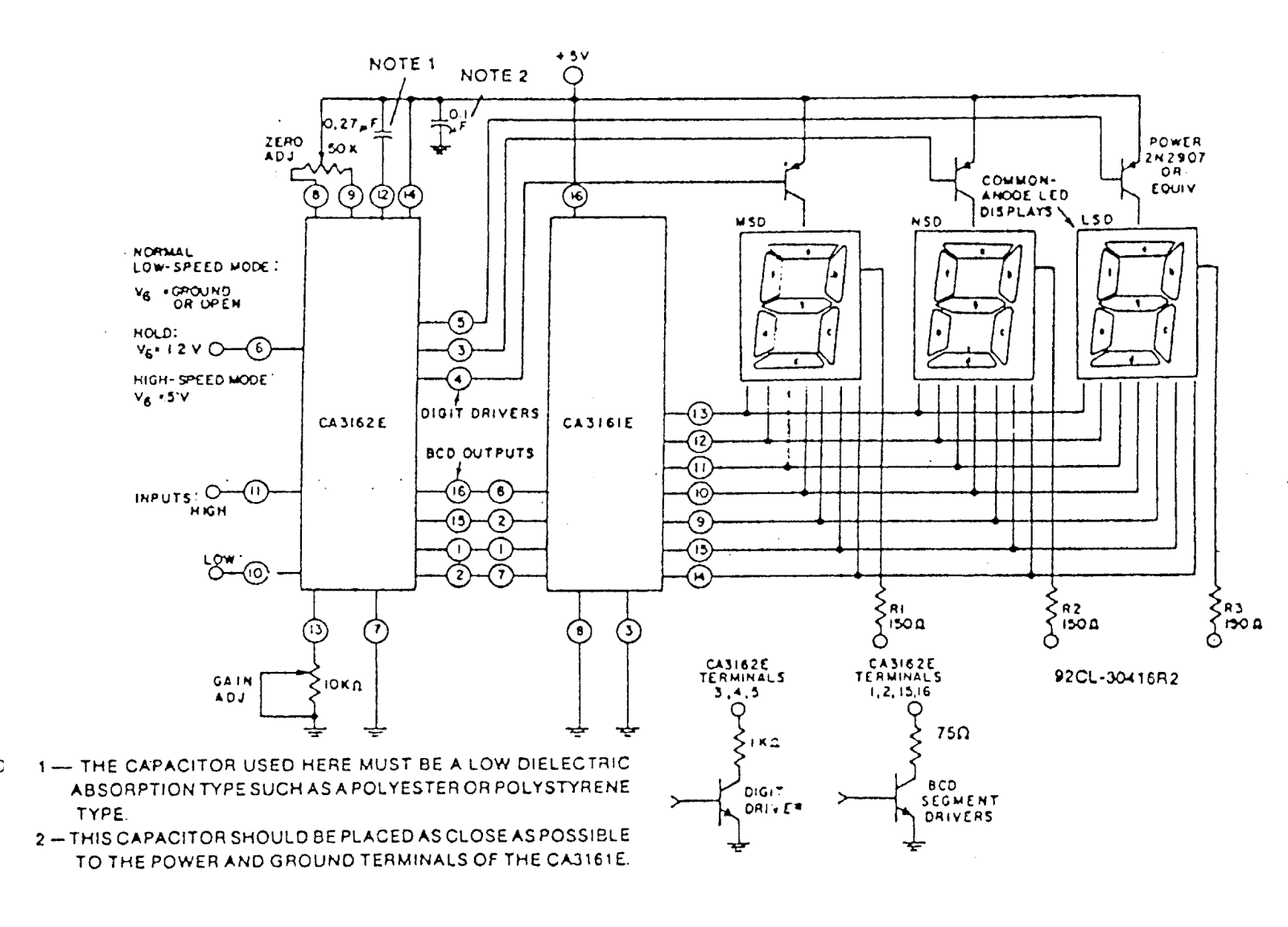

Application : Voltmètre numérique.

Analyse du fonctionnement.

Lorsque l'adresse 0 1 est envoyée sur les multiplexeurs, ceux-ci dirigent vers les afficheurs 7 segments les quatres sorties du compteur des unités et le démultiplexeur commande le transistor Tu, ceci permet de valider l'afficheur des unités, le décodeur DCB / 7 segments n'agira donc que sur cet afficheur.

Ensuite, l'adresse 1 0 apparaissant, ce sont les dizaines qui s'affichent puis les centaines avec l'adresse 1 1. Si la succession des adresses est suffisament rapide, l'utilisateur à l'impression que tous les afficheurs sont allumés simultanément.

Intérêts de ce système.

- 7 broches du circuit sont utilisées au lieu de 1 2 sous forme parallèle. - 1 décodeur, 7 résistances et 3 transistors sont utilisés au lieu de 3 décodeurs, et 21 résistances sous forme parallèle.

- Un seul afficheur est allumé au lieu de 3, ce qui limite légèrement la consommation.

visiter nous à la prochaine science

0 التعليقات

0 التعليقات